# TIMING SYSTEM FOR THE PEFP 100-MeV PROTON LINAC AND **MULTIPURPOSE BEAM LINES\***

Young-Gi Song<sup>#</sup>, Kyung-Tae Seol, Hyeok-Jung Kwon, Ji-Ho Jang, and Yong-Sub Cho Proton Engineering Frontier Project, Korea Atomic Energy Research Institute

#### Abstract

The PEFP 100-MeV Linac requires precision synchronization of timing trigger signals for various accelerator and diagnostic components. A timing event system is selected as the main timing system, which is operated based on an event distribution system and can be constructed with COTS hardware. This system broadcasts the precise timing information globally. Additional requirement is that this system must include the existing PEFP timing system which is implemented by using pulse delay generators. This paper describes the architecture, construction and performance of the PEFP timing event system.

#### **INTRODUCTION**

The Proton Engineering Frontier Project (PEFP) is constructing a 100-MeV proton Linear Accelerator (Linac), consisting of a 50-keV proton injector, Low Energy Beam Transport (LEBT), a 3-MeV Radio Frequency Quadrupole (RFQ), a 20-MeV Drift Tube Linac (DTL), 100-MeV DTL, and beam lines [1]. Since 2006, the 20-MeV proton linac already was developed with a beam line in KAERI. For 20-MeV linac, the timing system consists of commercial delay generators and fanouts to provide triggers for beam diagnostics, the ion source and Radio Frequency (RF), and modulators. The delay generator based timing system was limited to the 20-MeV linac and a standalone beam line. It has several drawbacks like synchronization with RF and AC main frequency. The event timing system will replace all the delay generators and other smaller parts to improve reliability and easy programmable functions. The improvement of the timing system for 100-MeV and multipurpose beam lines includes the upgrade to the Micro Research Finland (MRF) EVG-230/EVR-230RF with RF and AC main frequency [2].

### SYSTEM OVERVIEW

The PEFP has five beam extraction lines at 20-MeV and 100-MeV for proton beam utilization respectively. Figure 1 shows the extraction beam lines for 20-MeV and 100-MeV proton beams. The proton beam is extracted by a bending magnet and distributed to each beam line by a switching AC magnet. Timing system should deliver the trigger signals for synchronized beam pulses of the ion source, the modulator, the RF system, the beam diagnostic devices, and AC magnet power supply. Figure 1 shows the PEFP 100-MeV linac and multipurpose beam lines.

Figure 1: PEFP 100-MeV Linac and extraction beam lines

The timing system should have the functions including clock synchronization between sub-systems, RF gate generation, beam gate generation, triggering for beam diagnostics, AC magnet gate generation. Most triggers require TTL levels terminated into 50  $\Omega$  and a few optical links. All triggers should have low jitter performance of a few hundreds of picoseconds.

# TIMING SYSTEM USING DELAY **GENERATOR**

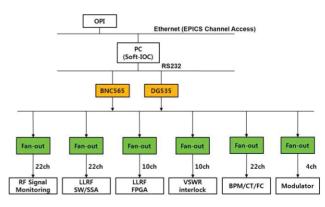

The current timing is composed of the pulse delay generators, including DG535 from Stanford Research Systems, BNC565 from Berkeley Nucleonic Corporation, and fan-outs which distribute a trigger delivered from the delay generator. The architecture of current timing system is shown in Figure 2.

Figure 2 Architecture of present timing system

The stability can be improved by changing the DG535 from an internal to an external reference signal of a 10 MHz reference clock supplied by the master oscillator. However, this timing system has a defect that is to a provide a clock and signal fixed to fan-out devices. It means the fan-out distributes the fixed delay and width on

<sup>\*</sup> This work is supported by the 21C Frontier R&D program in the Ministry of Science and Technology of the Korean government. # ygsong@kaeri.re.kr

a timing signal received from a delay generator, not changeable on each channel.

Therefore, the timing system is required to improve the performance of the timing system and to deliver the timing signals to the accelerator facility and beam lines. Event system was considered as a main timing system which can be triggered out of different clocks with a very low jitter. The event system has various types of outputs to avoid external level converters.

#### **EVENT TIMING SYSTEM**

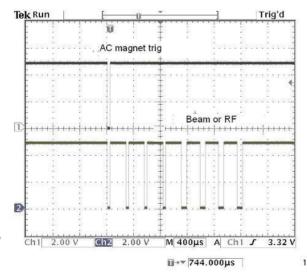

Preliminary test with the EVG/EVR-200, which is developed by the APS (Advanced Photon Source), was performed. Figure 3 shows a test system with VME event system. The event system characterizes the global distribution of timing signals to be accurate and flexible, providing multiple outputs. Figure 4 shows pulses generated by detecting rising edge of an external signal source. As a result of the performance and stability of the event system, the upgraded event system, EVG/EVR-230, was decided for PEFP timing system.

Figure 3 Preliminary test system using EVG/EVR-200 for timing system

ISBN 978-3-95450-115-1

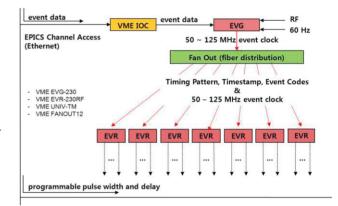

The upgrade timing system consists of a VME-EVG-230, seven VME-EVR-230RFs with RF recovery, a VME-FOUT-12, TTL and optical fiber output modules. The event system is based on time-multiplexed transmission of event codes. As a main system, an event generator transmits 8-bit event codes at the frequency from 50 to 125 MHz over an optical link. Thus, the time resolution is from 20 ns to 8 ns. The bit stream is distributed to event receivers via fan-out modules. The event receiver decodes the received event codes and performs the appropriate actions that are programmed for each event of interest to the particular crate.

Event generator generates events in response to external triggers from internal programmable event sequence RAMs or from VME bus writes. The event receivers were programmed to generate and send both pulse and set/reset level outputs. The EVG has two 512 Kbytes sequence RAMs, each of which can be enabled to transmit its contents to an external trigger of the event receivers. The sequence RAM is finally used as a trigger clock for the sub-components. After receiving event code and data, the event receivers can respond to the incoming event codes in different ways as well as recover the status of the signals on the distributed bus. The receivers has real transition module combined with 16 TTL output units. Figure 5 shows the architecture for the upgrade timing system.

Figure 5 Architecture of upgrade timing system

# APPLICATION

EPICS (Experimental Physics and Industrial Control System) IOC (Input Output Controller) of the timing system could be used with the driver and modules supported by EPICS community and integrated with PEFP control systems [3]. For EVG/EVR-200, the device drivers supported by EPICS community are modified to satisfy the operating mode. The application software was made on the modular the "eg" and "er" of the EPICS record/device supports, which mainly interact with the registers mapped on the VME memory. The CA (Channel Access) environments in the core of the EPICS were programmed for operator access. The original event system hardware was designed to look like the event system hardware used at Argonne by the APS, which is

> 07 Accelerator Technology and Main Systems T24 Timing and Synchronization

where the 14 delay/width pulses, the 4 extended delay/width pulses, the 7 flip-flop pulses, and the 7 trigger event pulses came from. The software was designed to use the egRecord and erRecords, which reflected the APS event system as well [4]. The Modular Register Map (MRM) system was created to supply a more uniform approach to the pulse generation. Instead of having four types of pulse, there are now 16 pulses, all of the same type, which can be programed to use either delay/width or flip-flop, making it a much more flexible system, but was almost completely incompatible with the egRecord and erRecord. Instead of writing new egRecord and erRecord versions, the new driver was decided to implement the software support using only standard EPICS records, which include ai, ao, bi, bo, longin, longout, mbbi, mbbo, etc [5]. This has the added advantage of allowing new features to be added without requiring that everyone rebuild all their databases. All of the logic in the event generator and event receiver modules is done in an FPGA. which means that the same hardware can be used to implement either the original register map (APS) or the modular register map. It just depends on which bitmap is loaded onto the FPGA, which can easily be done over the network. Operator Interface (OPI) is used with EPICS extension applications such as EDM (Extensible Display Manager) and python tool.

### CONCLUSION

The PEFP timing system is about to be upgraded from

a pulse delay generator system to a complete event system with multiple stations distributed via fiber optics around the machine and to the beam lines. The upgrade is intended to cover the increasing demands of users, to provide better flexibility and performance, and to reduce jitters. The EVG/EVR cards will be deployed throughout the facility to replace all delay generators and fan-out systems. The control software of the EVG and EVRs, including user interfaces, will be improved to conform to the requirements.

#### ACKNOWLEDGEMENTS

This work is supported by the Ministry of Education, Science and Technology of the Korean Government.

#### REFERENCES

- [1] Y. S. Cho, H. M. Choi, S. H. Jan, I. S. Hong, J. H. Jang, H. S. Kim, K. Y. Kim, Y. H. Kim, H. J. Kwon, K. T. Seol, and Y.G. Song, Test Result of the PEFP 20-MeV Proton Accelerator, EPAC 2006, p. 1609.

- [2] Jukka Pietarinen,"VME Event Reciever (VME-EVR-230RF), Event Generator, Technical Reference", 2011.

- [3] Martin R. Kraimer: "EPICS IOC Application Developer's Guide, "APS/ANL, 1998

- [4] John Winans (APS), Timo Korhonen (SLS), Babak Kalantari, "The Global Event System"

- [5] Michael Davisaver, Eric Bjorklund, Jayesh Shah, "MRF EVG/EVR Usage Guide", June. 2011, Rev. 5