# DEVELOPMENT OF A NEW CONTROL SYSTEM FOR THE FAIR ACCELERATOR COMPLEX AT GSI

R. Bär, U. Krause, V. Schaa, M. Thieme, W. Schiebel, GSI, Darmstadt, Germany

### Abstract

The 'Facility for Antiproton and Ion Research' (FAIR) will be realized at the 'GSI Helmholtzzentrum für Heavy Ion Research' (Darmstadt, Germany) in the scope of a large international organization. This new accelerator complex will be a significant extension to the existing GSI accelerator chain. It will present unique challenges for the control system which are well beyond the capacity of the present system. A new control system is under development that considers all aspects of the expected functionality to operate the GSI/FAIR machines and integrates the present GSI controls infrastructure. The new control system substantially builds on proven principles and solutions and is based on a strictly modular design with well defined interfaces. Size and organizational structure of the FAIR project with international contributions demand for a high level of standardization and efficient interface management. This report summarizes concepts, architecture, technologies and building blocks of the new system.

## THE FAIR ACCELERATOR COMPLEX

With the accelerators UNILAC, SIS and ESR an in many aspects worldwide unique accelerator facility for heavy ion beams is presently operated by GSI. In 2001, GSI, together with a large international science community, put up a proposal for a new accelerator Facility for beams of Antiprotons and Ion Research (FAIR) that uses the existing machines as injector chain [1]. Since then and after multi-annual planning and preparation the project has gone through major steps of development. Significant progress has been achieved with respect to scientific-technical and political preparation of the project [2].

The layout of FAIR is shown in Figure 1. The central part of the FAIR facility is a synchrotron complex consisting of two separate superconducting synchrotron accelerator rings with a maximum magnetic rigidity of 100 Tm and 300 Tm. A new proton-linac will provide high current proton pulses for the anti-proton production chain. In addition to several fixed beam experimental stations, anti-proton and rare-isotopes production and separation systems, the facility will be complemented by a system of cooler and storage rings (CR, RESR). Experimental storage rings for high (HESR) and low (NESR) energy range are provided for high-precision inbeam experiments.

To overcome the problem of a significant cost increase for the full project it is foreseen to start FAIR in a staged and modularized concept that takes into account performance and scientific excellence of the served physics experiments. After the official launch of the FAIR start version was already celebrated in November 2007, the final project start is expected for the next months to come. Start of civil construction building activities are expected in fall 2010. Commissioning of the first FAIR systems is expected for the year 2015.

Figure 1: The layout of FAIR. Parts of the existing facility (blue) act as injector for the new FAIR facility (red).

## THE CONTROL SYSTEM: DESIGN CONSIDERATIONS

The existing control system at GSI is well adapted to the present needs but because of new and much higher technological requirements, scalability, data acquisition performance and obsolete hardware the need of a new system is obvious. Due to strict boundary conditions in respect to manpower, time schedule, costs, involvement of partners, the strategy of implementing new systems has to be most effective. Due to the international character with in-kind contributions of FAIR partners a strict policy of standardization of interfaces and software developments are of utmost importance [3].

On the technical level the FAIR control system is not fully defined yet. It is presently in the technical design phase, keeping well working principles while adopting new methodologies where beneficial.

The control system will be designed as a decentralized distributed system and based on a strictly modular design with well defined interfaces which will allow breaking down the project in interconnected work packages that can be implemented independently. It will be based on the highly accepted operating system Linux, widespread programming languages such as C++ and Java and has to support most common hardware technologies.

An important consideration was to learn from best practices in other control systems and trying to identify proven solutions that could adequately be used as building blocks to the FAIR control system in order to reduce the development effort and possibly profit from collaborations. Since CERN and FAIR have similar requirements concerning the control of accelerators, a closer look on the CERN control system solutions was taken. Several fields of implementation have been identified and studied as described below and successful collaborations have been initiated. Further development on the FAIR control system can be concentrated on the missing functionality, particular solutions for FAIR requirements, and on integration and functional extension of those control system building blocks selected.

#### THE FRONTEND SOFTWARE: FESA

Device software running on front-end computers to monitor and control accelerator devices is a central part of the new control system for FAIR. After evaluation it was decided to adopt the Front-End Software Architecture (FESA) that was developed by CERN and is already well established for LHC and its injectors [7]. FESA is a software framework that provides a full environment and tools to design, develop, implement, test and deploy device software. It is not only optimized for device control but also for data acquisition performance. FESA was developed with the objective to standardize, speed-up and simplify the task of developing front-end software.

While also an in-house development of a similar system has been considered, the main reason to adopt FESA is the high level of maturity and availability of the system at this time. Consequently, specifications for FE systems can be precisely defined and training of staff and in-kind contributing FAIR partners can be started early in the project. The decision to use FESA leads to a high level of standardization of the supported environment.

Apart from the things in common, there are also differences between CERN and GSI control system implementation, accelerator structure, etc. These differences do not allow direct use at GSI. Collaboration between CERN and GSI offered a solution to the problem: GSI temporarily relocated two developers to CERN to contribute to the development of a new completely redesigned FESA version. Although most CERN users of FESA are content with FESA 2.10 CERN will also profit from the new features that will be implemented in FESA 3.0. Features needed by both institutes are contained within the new FESA 3 framework. The wish to also cover functionality that is specific to CERN or GSI has led to the introduction of the laboratory package concept. Using this concept the split into two different framework branches can be avoided, resulting in greater synergy effects and less work for both institutes.

#### EQUIPMENT DEVICE CONTROLLER

Most accelerator devices (e.g. all power converters and rf-systems), explicitly excluding beam instrumentation data acquisition systems, will be interfaced and controlled by a dedicated and cost-effective front-end controller (FEC) that is presently under development and component validation. Details are presented in [6].

The main components of the distributed intelligent peripherals are a highly integrated commercial computeron-module (COM) and a powerful FPGA. By providing more than adequate computing and hardware logic resources for even demanding equipment control, the system is named Scalable Control Unit (SCU) and defined as one principal control standard for the FAIR project. The control system FE software (FESA) runs under standard Linux OS on the CPU. High precision time critical functions, e.g. a function generator for ramps, integrated timing system receiver, are realized directly on hardware level (VHDL).

SCUs will be generally integrated in the equipment (e.g. power converter cabinet) to be controlled. Form factor and equipment interface connector have been defined in a way to provide maximum compatibility with present equipment systems at GSI for seamless integration and easy upgrade. A mechanical model of the SCU is shown in Figure 2.

Figure 2: Mechanical model of the SCU.

Primary interface to the controlled equipment is a dedicated 32-bit wide bidirectional parallel bus interface (SCU-bus) which is a further development of an existing in-house bus system and allows seamless transition of presently developed equipment. In addition, up to four serial high-speed links (>500 Mbit) are foreseen for future applications. Three Ethernet connectors (100/1000 Mbit) are provided as interface to the higher control layers and the general machine timing system.

#### **MACHINE TIMING SYSTEM**

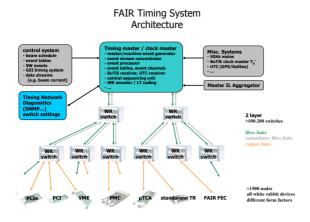

The primary task of the General Machine Timing (GMT) system is to trigger and synchronize equipment actions, timed according to the accelerator cycles and beam transfers. The GMT is implemented as an event based system that provides concurrency of events by transmission time compensation and absolute timestamps by synchronizing distributed clocks. For high-precision synchronization beyond the parameters of the GMT a dedicated bunch timing system will be used.

Figure 3: Architecture of the timing system.

The architecture of the GMT is shown in Figure 3. The GMT will broadcast centrally generated timing telegrams in a tree topology within a dedicated timing network. Transmission is based on Gigabit Ethernet technology using fiber and copper transmission lines and the new 'White Rabbit' (WR) protocol which is a result of collaboration between different institutes and companies, mainly CERN and GSI [4]. The WR protocol is a lowlevel timing and control transport protocol for WR network devices on level 2 of the OSI reference model. It provides reliable one-way transmission channels, precise delay measurements and sub-ns transparent time transmission based on a novel combination of Precision Time Protocol and Synchronous Ethernet standards. Since no loss of events is acceptable, forward error correction algorithms will be implemented.

A master beam sequencer (MBS) will coordinate and orchestrate all beams and cycles throughout the GSI/FAIR accelerator complex. Dedicated timing event generators (EVG) generate all timing events for a particular machine utilizing internal counters, event sequencers and hardware inputs. Special OSI layer 2 switches, called WR switches, are presently developed implementing the WR protocol standard. Event receivers (EVR), provided in all relevant form factors, decode the event stream and provide hardware outputs or software interrupts based on event content. EVR must be WR compliant devices in order to be able to receive and decode timing telegrams.

### ACCELERATOR SETTING GENERATION AND MANAGEMENT

Central part of the FAIR control system on business logic layer is the component for generating and managing settings for accelerators and the whole accelerator chain. Getting data from devices through middleware systems, keeping static data about the accelerator, and presenting all contained information in an integrated way to the application layer is the main focus of this component. After evaluation by GSI controls and machine physics groups it was strategically decided to adopt the LSA framework from CERN as central component for the new FAIR control system [5].

Status Report

LSA (LHC Software Architecture) is a working solution for settings management and data supply which was designed with the objective to provide very generic solutions that could be easily re-used and extended for several accelerators. The settings management component represents the basis for applications. It therefore defines and provides a clear, simple interface through which applications can easily access relevant data. LSA itself is written in Java using the Spring framework.

LSA provides a clear separation between data model, business logic and applications. Being built in a modular way, institute specific implementations can be easily plugged in. Central aspect of LSA is that an accelerator is modeled by describing its parameter hierarchy – from top level physics parameters down to hardware parameters. LSA system provides different functional building blocks which, among other benefits entitles machine physicists to implement the machine model in a structured and simple way.

Cooperation between CERN and GSI started in 2007 with the temporary relocation of two GSI developers into the CERN LSA core team. Since 2009 a well working and fruitful collaboration was set up with joint development effort put into future LSA development. Restrictions of the system were overcome and additional requests for flexibility and functionality were already implemented into the LSA core base. A future topic to be addressed will be the modeling of a chain of accelerators including modeling inter-accelerator dependencies, which are necessary for FAIR. Since at CERN also the focus shifts towards controlling the full accelerator chain, mutual objective of both parties is to provide a generic and as flexible as possible framework for all aspects of accelerator operation.

#### REFERENCES

- [1] D. Krämer et al., "Current Status of the FAIR Project", THXAB02, PAC 2007, Albuquerque, USA.

- [2] H. Stöcker, "FAIR: Challenges Overcome And Still To Be Met", MOYCGM01, EPAC 2008, Genoa, Italy.

- [3] R. Bär, U. Krause, V. Schaa, P. Schütt, "The New FAIR Accelerator Complex at GSI: Project, Controls Challenges and First Steps", TOAB01, ICALEPCS 2007, Knoxville, Tennessee, USA.

- [4] J. Serrano et al., "The White Rabbit Project", TUC004, ICALEPCS 2009, Kobe, Japan.

- [5] J. Fitzek, R. Müller, D. Ondreka, "Evaluation of the LHC Software Architecture for Data Supply and Setting Management within the FAIR Control System", THP012, ICALEPCS 2009, Kobe, Japan.

- [6] M. Thieme, M. Zweig, S. Rauch, W. Panschow, "Single Board Computer for Equipment Control", TUP060, ICALEPCS 2009, Kobe, Japan.

- [7] T. Hoffmann, "FESA The Front-End Software Architecture at FAIR", WEP007, PCaPAC 2008, Ljubljana, Slovenia.