# **ASYNCHRONOUS DRIVER EVALUATION AND DEVELOPMENT** FOR DIGITAL SYSTEMS AT THE ARGONNE TANDEM LINEAR ACCELERATING SYSTEM\*

C. E. Peters<sup>†</sup>, J. Reyna, D. Stanton, Argonne National Laboratory, Lemont, USA

# Abstract

title of the work, publisher, and DOI The ATLAS (Argonne Tandem Linear Accelerating System) accelerator at Argonne National Laboratory, near author( Chicago, IL., has recently been upgraded via the addition of a pulsed mode Electron Beam Ion Source (EBIS). Pulsed operation requires finer levels of control of various E plies and remotely controlled function generators. Addi-tionally, pico-level and femto-level ammeters need per-de-tivice zero correction and calibration to accurately read beam intensities. As the facility moves away from fast regnaintain ister-based analog signals, new and slower digital protocols adversely affect the perceived execution time of the control system. This work presents options, research, and results of implementing an asynchronous layer between high level user interfaces and the low level communication drivers in order to increase the perceived responsiveness of : the system. Solutions are evaluated ranging from in-house  $\frac{1}{2}$  codes, which implement system-wide mutual exclusion and prioritization, to drivers available from the EPICS conuo trol system. Key performance criteria include ease of im-plementation, cross platform availability, and overall ro-bustness. Any

#### **INTRODUCTION**

2019). The ATLAS accelerator is located at the United States Department of Energy's Argonne National Laboratory in Q the suburbs of Chicago, Illinois. It is a National User Falicence cility capable of delivering ions from hydrogen to uranium [1] for low energy nuclear physics research in order to perform analysis of the fundamental properties of the nucleus. The majority of the current control system has been based β on a CAMAC Serial Highway [2] (SH) architecture since 20 the 1980s. Access to this hardware bus from software relies on PCI based personality cards which in turn connect of to the serial highway. While this system is clearly outdated terms from a technology progress perspective, it continues to provide distributed serial networking with low latency and high reliability. This improves the perceived responsiveunder ness of the control system and allows simple singlethreaded access via the use of the operating system's regused ister-based PCI subsystem interface.

Moving away from CAMAC and fast register access has þ scommonly been accomplished by interfacing to (non-Ë CAMAC) serial devices in the form of USB/RS-232/RSwork 485 specifications. However these devices use slower baud rates and typically control more complicated devices. This this

```

WEPHA119

```

results in longer latency delays for each command. It should be noted this application is for a 'slow' control system and all values are only updated at about ~1-2Hz.

## ATLAS Control System Software Description

The ATLAS Control System (ACS) group only consists of 2-5 full-time members, depending if the definition includes students and temporary assignments. Therefore, a third-party vendor Vista Control Systems, Inc. [3] is used to provide software libraries to supplement the creation of database structures, operator interfaces, logging tools, etc. The EPICS control system is acknowledged to be the largest and most comprehensive offering in the space, however the amount of overhead to implement and maintain a large and diverse open-source package can be prohibitive for small groups. Even borrowing individual modules like the EPICS Asyn driver [4] can be resource prohibitive unless the group has already committed to the full EPICS ecosystem.

### **BENCHMARKS**

In order to implement a modern solution to register base CAMAC which do not cause the main operator interface (OPI) to lock, we need to understand the current level of latency in the existing software/hardware loop.

#### CAMAC/PCI/OPI Latency

- Single core 400 MHz Alphaserver 1200 CPU running OpenVMS 8.2 with idle CPU usage and 1GB memory.

- Kinetic Systems 2115 PCI Serial Highway Driver running in byte-wise mode at 2.5MHz clock speed

- Single 16-bit CAMAC NAF Operations

| Т | able | I: CAN | ЛАС Е | execution | Latencies |   |

|---|------|--------|-------|-----------|-----------|---|

|   |      |        |       |           |           | _ |

| Operation     | # of Calls | Time    | Latency    |

|---------------|------------|---------|------------|

| 16-bit Read   | 1,000,000  | 47 sec  | 47 μSec    |

| 16-bit Write  | 1,000,000  | 47 sec  | 47 μSec    |

| Fast Process* | 100,000    | 38 sec  | 380 µSec   |

| OPI Slider    | 5000       | 262 sec | 5,240 µSec |

\* A Data acquisition process running at its fastest software loop

# *Non-CAMAC Serial Latency*

It is noted here that raw CAMAC latency is quite low (see Table 1). This will be difficult to match. However as more and more software overhead is added, the latency for each loop of software adds to the hardware latency, and the actual required latency of any replacement system becomes more reasonable. The fastest process running on the SH is only about 0.5msec of latency, and the human interfaces

from \* This work was supported by the U.S. DOE, Office of Nuclear Physics, under Contract DE-AC02-06CH11357. The research used resources of Conten ANL's ATLAS Facility, a DOE Office of Science User Facility. † ChrisPeters@anl.gov

17th Int. Conf. on Acc. and Large Exp. Physics Control Systems ISBN: 978-3-95450-209-7 ISSN: 2226-0358

(sliders) execute 10 times that at ~5 milliseconds. Table 2 represents latency testing on alternatives to CAMAC serial highway communication architectures.

These times can now be compared to modern serial:

- Single core Intel Pentium 4 at 2.8GHz running Scientific Linux 6.7 with idle CPU usage and 1GB memory.

- Weiner CC-USB CAMAC Crate Controller

- Linux TCP/IP Packets with 16-bit payload.

Table 2: Non-Camac Serial Execution Latencies

| Operation     | # of Calls    | Time    | Latency     |

|---------------|---------------|---------|-------------|

| 16-bits@57600 | (theoretical) | N/A     | 277 µSec    |

| USB CAMAC     | 1,000,000     | 265 sec | 265 µSec    |

| TCP@100Mbit   | 1,000,000     | 293 sec | 293 µSec    |

| Keithly6514   | (single read) | N/A     | 30,000 µSec |

The overall conclusion of this testing is that the existing CAMAC latency is in the ~40 $\mu$ Sec range and modern serial replacements are about an order of magnitude more. This drives motivation to develop our own set of software layers which provide multi-threaded support such that the operators do not notice a significant increase in lag.

# **ASYNCHRONOUS SOLUTION**

We can now assemble a list of requirement for our new software layer which will enable highly responsive applications for this specific set of ACS software libraries.

#### Requirements

The software solution should be simple and be based primarily on Linux, as this is the common operating system of the ACS. It should use native operating system primitives to accomplish locking and memory sharing. In addition, this layer should be aware of priorities of executing threads determined by assigning a write higher priority than read. In general the C language is used unless there are specific object-oriented runtime advantages.

#### Architecture

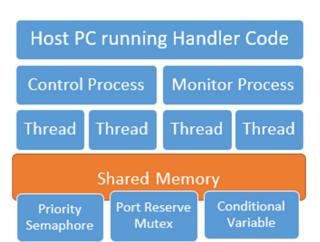

It is important to note that VSystem is based on a remote procedure call (RPC) signalling system which spawns multiple processes accessing a single channel. Therefore there are 2 processes running handler code as shown in Figure 1.

#### Shared Memory Port Locking Algorithm

There are two sets of procedures depending on if the call to the serial handler is a high priority or a low priority. At this time, there are only 2 implemented priorities. In the example below, the main OPI thread spawns a worker thread and immediately returns, allowing the user to continue interacting with other devices or functions.

In summary, a high priority thread needs to reserve only the mutex, but a low priority thread has to reserve both the mutex and the semaphore thereby causing a higher probability the higher thread will execute first. ICALEPCS2019, New York, NY, USA JACoW Publishing doi:10.18429/JACoW-ICALEPCS2019-WEPHA119

maintain attribution to the author(s), title of the work, publisher, and DOI.

must

work

of this v

Any distribution

19).

20]

0

licence (

3.01

ВΥ

2

the (

Content from this work may be used under the terms of

Figure 1: Hierarchy of key software components.

# Higher Priority Thread

- 1. Call "sem\_wait" on a semaphore in shared memory to signal other threads a high priority thread is waiting.

- 2. Once semaphore is locked, it signals that other lower priority threads have paused and we are clear to run.

- 3. Attempt to lock shared memory's port mutex to acquire rights to the shared serial port.

- 4. Now that we have acquired the port, "sem\_post()" the high priority semaphore to signal no longer waiting.

- 5. Do long running serial transaction....

- When done, call pthread\_cond\_broadcast() on the semaphore to wake up sleeping low priority threads.

- 7. Finally, unlock the port mutex to release the port.

# Low Priority Thread

- 1. Block on attempting to lock shared memory's mutex to acquire rights to the port (note: no semaphore lock).

- 2. Call sem\_getvalue() to determine if there is currently a higher priority thread waiting, if not do transaction.

- 3. If the value returned by sem\_getvalue() is zero, then enter a conditional wait loop. The conditional wait also releases the mutex allowing other processes run.

- 4. Get woken up by a signal from high priority thread when the port mutex is acquired by our process.

- 5. Once the high priority semaphore is non-zero, do long running serial transaction.

- Call pthread\_cond\_broadcast() on the semaphore to wake up any other sleeping low priority threads.

- 7. Finally, unlock the port mutex to release the port.

### Shared Memory Layout

A note about shared memory is that it is assumed any process has already acquired a pointer to this section by supplying a common handle identifier across processes.

struct stSharedMemVars

{ pthread\_mutex\_t mutex; pthread\_cond\_t conditionVar; sem\_t semHighPriority;

The purpose of the mutex is to represent "mutual exclusive" access to a resource like a serial port. The purpose of

17th Int. Conf. on Acc. and Large Exp. Physics Control Systems ISBN: 978-3-95450-209-7 ISSN: 2226-0358

the condition variable is to signal low priority threads to sleep and be woken up asynchronously when a higher pripublisher, ority thread completes. The purpose of the high priority semaphore is to maintain a count of the number of processes system wide that are high priority, and then asynwork. chronously signal the other processes to wake-up and resume attempting to lock the shared resource (port). author(s). title of the

## **IMPLEMENTATION AND TESTING**

The asynchronous and multi-threaded method described above has been implemented in the ACS in two different pieces: 1.) An example high-level handler for Keithley Picoammeter 6514 device driver has been re-written such that blocking calls to the lower serial layer are moved to their own "threadEntry" function with new calls to spawn their own "threadEntry" function with new calls to spawn of those threads, and 2.) The lower level serial device code has been modified to implement the locking algorithm based on shared memory described in the "Algorithm" sections above. maintain

\*\*For the following tests an artificial 0.5 second delay was added to the serial port driver to simulate a particularly low baud rate or long running process.\*\*

- Send Qty 4 high priority commands to the device simultaneously, verify main thread returns quickly.

- Send Qty 4 high priority commands to the device simultaneously, and verify the low priority threads wait.

```

Thread Index[0] = Chix 18, Thread ID b5a80b70

PARENT THREAD Returned in 0.000081 seconds.

Thread Index[1] = Chix 19, Thread ID b4cffb70

PARENT THREAD Returned in 0.000126 seconds.

Thread Index[2] = Chix 20, Thread ID b42feb70

PARENT THREAD Returned in 0.000130 seconds.

Thread Index[3] = Chix 21. Thread ID b82fdb70.

IEW

NEW

Thread Index[3] = Chix 21, Thread ID b38fdb70

PARENT THREAD Returned in 0.000131 seconds

T TO TO

0.500521 seconds for command SENS:CURR:RANG 2E-6

0.507705 seconds for command :SYST:ERR?

hread Done: ID b5a80b70

0.500523 seconds for command SENS:CURR:RANG 2E-5

0.507940 seconds for command :SYST:ERR?

Thread Done: ID b4cffb70

0.500524 seconds for command SENS:CURR:RANG 2E-4

Thread Done: TD b42feb70

0.500524 seconds for command SENS:CURR:RANG 2E-3

0.507998 seconds for command :SYST:ERR?

```

Figure 2: Main OPI thread returns in <1mS.

ICALEPCS2019, New York, NY, USA JACoW Publishing doi:10.18429/JACoW-ICALEPCS2019-WEPHA119

| P controlsys@acs082:/atlas/programs/ATLAS_Native_Serial_Handlers |         |       |   |  |

|------------------------------------------------------------------|---------|-------|---|--|

|                                                                  |         |       |   |  |

| Thread Done: ID b53ffb70                                         |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         | onds. |   |  |

| 0.830733 seconds for command REA                                 | D?      |       |   |  |

| Thread Done: ID b49feb70                                         |         |       |   |  |

| WARNING - Thread b53ffb70 sleeping insid                         | e Cond. | Wai   | t |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| WARNING - Thread b53ffb70 sleeping insid                         |         |       | ÷ |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| WARNING - Thread b53ffb70 sleeping insid                         |         |       | ÷ |  |

| MARNING - Thread b49feb70 sleeping insid                         |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| MARNING - Thread b53ffb70 sleeping insid                         |         |       | + |  |

| MARNING - Thread b49feb70 sleeping insid                         |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| MARNING - Thread b53ffb70 sleeping insid                         |         |       | + |  |

| MARNING - Thread b49feb70 sleeping insid                         |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| PARENT THREAD Returned in 0.0000                                 |         |       |   |  |

| 0.510531 seconds for command SEN                                 |         |       |   |  |

| 0.510551 seconds for command ser                                 | S.CORR: | MANG  |   |  |

Figure 3: Low priority threads sleeping.

Figure 2 is a debugging printout from the higher priority control process. Here we can see 4 threads being spawned with different thread IDs. Next, we see one thread at a time acquire a lock on the serial port and execute several longrunning commands which would normally block the parent thread. At the bottom we see each thread in turn complete with no errors. Additionally, the parent thread returns generally in the microsecond range.

At the same time this is happening, Figure 3 shows a second monitor process polling 2 values from the device. When the high priority threads run, the block execution of the lower priority threads. We can see the low priority threads sleeping, but still returning control to the calling thread within several microseconds. Eventually the low priority threads get released from their conditional wait and begin sending messages once again.

#### CONCLUSION

The purpose of this work is to implement asynchronous and priority based threading on top of the regular serial port driver code. While this type of layer is common in control systems like EPICS which have a single process per port, it does not come for free on other software packages. We have demonstrated that by using a combination of shared memory space, shared mutex and condition variables, and careful thread management, a similar feature to EPICS Asyn can be implemented and drastically decreases perceived execution time of the control system to lower than at least the ~13mS theoretical latency of the human eye itself [5].

#### ACKNOWLEDGEMENTS

This work was supported by the U.S. Department of Energy, Office of Nuclear Physics, under Contract No. DE-AC02-06CH11357. The research used resources of ANL's ATLAS Facility, a DOE Office of Science User Facility.

the

5

must

distribution of this work

Anv

2019).

0

17th Int. Conf. on Acc. and Large Exp. Physics Control Systems ISBN: 978-3-95450-209-7 ISSN: 2226-0358

#### REFERENCES

- [1] "Stable Beams Available from ATLAS", www.phy.anl.gov/atlas/facility/stable\_beams.html, retrieved October 12, 2015.

- [2] IEEE Std. IEEE Std. 595-1982, Standard Serial Highway Interface System, The Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017.

ICALEPCS2019, New York, NY, USA JACoW Publishing doi:10.18429/JACoW-ICALEPCS2019-WEPHA119

- [3] Vista Control Systems, Inc. https://www.vista-control.com/

- [4] EPICS Asyn Driver, https://epics.anl.gov/modules/soft/asyn/

- [5] Potter, M.C., Wyble, B., Hagmann, C.E. *et al.*, Atten Percept Psychophys (2014) 76: 270. doi.org/10.3758/s13414-013-0605-z

**WEPHA119**

1371