### RF SYSTEM DEVELOPMENT FOR THE CEBAF ENERGY UPGRADE\*

C. Hovater<sup>†</sup>, P. Chevtsov, J. Delayen, H. Dong, L. Harwood, J. Musson, R. Nelson, T. Plawski, H. Wang, Jefferson Lab, Newport News VA, 23606, USA

Abstract

A planned upgrade of the present 6 GeV CEBAF accelerator at Jefferson Lab will increase its energy to 12 GeV. To achieve this, new 7-cell superconducting cavities are being built to operate at an average accelerating gradient of 19.5 MV/m with and external Q of 2.2 x 10<sup>7</sup>. The present RF system composed of an analog control loop driving 5 kW klystrons will not support the new cavities and their intended gradients. In light of this, we have been developing both a new RF control system based on a Self Excited Loop using digital feedback and a new high efficiency 13 kW Klystron. It is also intended to use the new RF system for both the Jefferson Lab IR FEL upgrade and the Rare Isotope Accelerator (RIA). This paper discusses these developments and reports on their progress.

### 1 RF SYSTEM REQUIREMENTS

The cavity field regulation is essentially determined by the electron beam energy spread requirements, which are 0.01% and 0.02% at 6 and 12 GeV respectively [1]. For the lower energies (< 6 GeV) these are unchanged from the original specification. This in turn drives the phase and gradient control specifications for the RF system. Presently the maximum errors allowed in the accelerator are 0.13° in phase and  $1.1x10^{-5}$  for amplitude [2].

These requirements must be met while the control environment for the RF system will be substantially different from that of CEBAF at 6 GeV. To optimize the required drive power, the new cavities' Qext will be increased to 2x10<sup>7</sup>. This Q<sub>ext</sub> minimizes the amount of RF power required to provide the design gradient (20 MV/m) to the required current (470 µA) with an expected peak detuning of 25 Hz (corresponding to a vibration-induced microphonics of 3.5 Hz rms and a 2 Hz frequency tuner resolution. The increased gradient and external Q has made the Lorentz detuning effect much more pronounced than the original design of 5 MV/m and 6.6 x 10<sup>6</sup>. It is expected that the detuning will be more than ten times the cavity bandwidth. In addition the decreased bandwidth has made the microphonics a larger factor than in the original system [3].

### 2 PROPOSED RF SYSTEM

All of this impacts the design of the new RF system. We have chosen to change from a Generator Driven Resonator (GDR) system with phase and amplitude analog feedback to a Self-Excited Loop (SEL) which will incorporate digital feedback. The Lorentz detuning

stemming from the high gradient when, combined with the narrow cavity bandwidth, results in a multi-valued detuning curve (it folds back upon itself); this condition makes the SEL an easier system to implement, especially since CEBAF is CW [4]. A GDR based system may have difficulty reaching gradient without a slow ramp or other compensation, which would decrease CEBAF availability. An SEL would not need such compensation and would track the detuning while the cavity fields ramp up to steady state.

The increased cavity gradient has increased the RF power requirement to 13 kW, which effectively means a new klystron design. A goal for the new klystron design is to increase the efficiency from ~ 35% to closer to 60%.

Eight years of operational experience with over 300 SRF systems have also provided us with a lot of practical experience and "lessons learned". The next generation system will be more user-friendly from a maintenance perspective, allowing an individual cavity/RF system to be taken off line for maintenance and repair with minimal beam interruption.

## 2.1 System Architecture

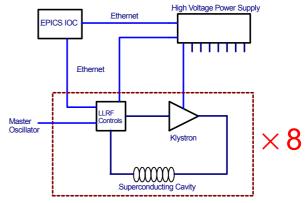

The present system uses one RF system per cavity and we do not plan to change this architecture which has allowed us to operate each cavity at its maximum operating gradient [3]. Each cryomodule holds eight cavities and existing controls and RF power system are based around building blocks of eight. One high voltage power supply will feed the eight klystrons. A failed klystron can be isolated from the system with only minor interruption to operations. The low level RF (LLRF) controls will also be independent from one another and communicate with the EPICS control system through an Ethernet connection via a local network. Figure 1 shows a block diagram of the RF system.

Figure 1: RF System Block Diagram

<sup>\*</sup>This work was supported by the U.S. Department of Energy Contract Number DE-AC05-84-ER40150

<sup>†</sup>hovater@jlab.org

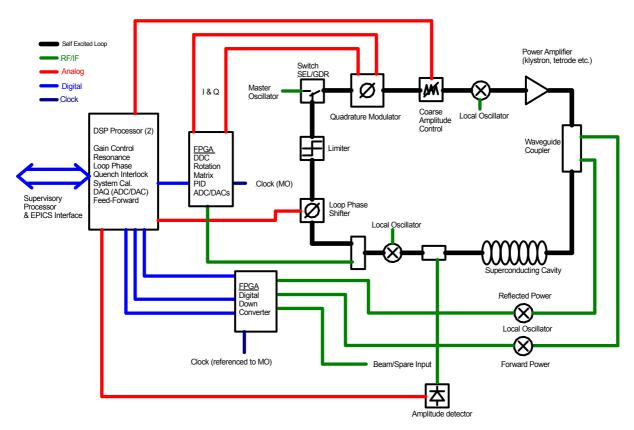

Figure 2: Low Level RF Block Diagram

# 3 LOW LEVEL RF (LLRF)

Figure 2 shows the conceptual block diagram of the proposed system. The SEL will be operated at the cavity frequency and then down-converted to an IF of 70 MHz for digital conversion and signal processing. This will allow the design, with the exception of a small section, to be generic and independent of the cavity. In particular it is expected that most of the design will be directly applicable to other high-Q CW accelerators such as RIA. In addition to the cavity-transmitted power, three other signals (forward, reflected, beam feedback/spare) can be digitally down-converted and processed for control.

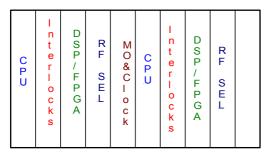

Figure 3 shows a mockup of what a VXI crate could look like with two LLRF systems. Each LLRF system will consist of four printed circuit cards.

Figure 3: VXI crate showing two LLRF systems

The CPU board will be either a Pentium or Power PC communicating directly with EPICS by way of Ethernet.

The CPU board will be the supervisory processor for the RF system, handling much of the slower processing (system interfaces, klystron, alarms, in situ calibration etc.). A cavity interlock board would contain the logic and signal processing needed to protect the cavity and associated components (coupler, window, vacuum, cryomodule). The digital feedback and signal processing will be incorporated in the DSP/FPGA board. The RF/SEL board would have the cavity-specific RF components (mixers, IQ modulators etc.). Finally, a master oscillator and clock module would be common to both LLRF systems. The "production" configuration of the LLRF system will include segmentation of the crate such that each LLRF system will have its own power supply and ground. In this way each system would then be hot swappable, thereby providing the opportunity for performing maintenance while the accelerator is operating.

Most of the RF/SEL section components have been prototyped and tested in various systems for instrumentation in the Jefferson Lab SRF Institute test facilities. One of the challenges so far has been to find a limiter with very little phase shift as a function of RF input. Because the communications & RADAR industries are increasing their use of digital receivers, the demand for RF or analog limiters has been greatly reduced, resulting in termination of production of several commercial components that we had tested and would have been useful to this project.

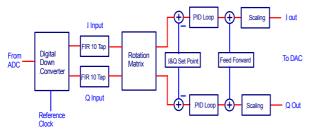

The digital down converter and feedback is implemented with an Altera Stratix FPGA. Supervising the feedback and other fast controls are two TI6711 digital signal processors (DSP), which we have already successfully used in other systems [5]. We have evaluated different implementations for the digital feedback section with respect to price, process delay and ease of design. We compared each hardware implementation using the same logic function block shown in figure 4.

Figure 4: LLRF Logic Functions

Table 1 is a comparison of the three different hardware implementations for digital feedback. As is industry, we are also investigating programmable gate arrays with DSP block sets. The increased speed and the ability to be more design-specific make these very attractive. Their only drawback is the relatively high price.

Table 1: Comparison of Digital Hardware Implementations

| DEVICE  | Number   | DSP    | Delay of  | Cost (units) |

|---------|----------|--------|-----------|--------------|

|         | of Logic | Blocks | logic     | 1,           |

|         | Elements |        | functions | 50-100,      |

|         |          |        | (uS)      | >100         |

| STRATIX | 1240     | 4      | .429      | \$885        |

| FPGA    |          | 64     |           | 645          |

|         |          |        |           | 605          |

| APEX    | 20000    | -      | .750      | 1880         |

| FPGA    |          |        |           | 1590         |

|         |          |        |           | 1380         |

| TI 6711 | -        | -      | 19.52     | 110          |

| DSP     |          |        |           |              |

Resonance control for the RF system will utilize a mechanical stepper motor and a piezoelectric tuner (PZT). The piezoelectric tuner will have ~ 1 Hz of resolution resulting in a time-averaged cavity-resonance stability of ~2 Hz. The control signals for the stepper motor will be processed by the CPU board. The PZT will need to incorporate faster processing so it will be controlled by the TI6711 DSP.

## **4 KLYSTRON**

The present CEBAF klystron is a 5 kW, four-cell, permanent magnet tube with efficiency of ~ 35%. We have been able to raise the power to 8 kW by increasing the cathode voltage but the tube operation becomes increasingly problematic beyond this (it was based on an air cooled 2 kW tube). For the CEBAF upgrade we will

need at least 13 kW of RF power to reach the required cavity gradient given the background microphonics and beam loading. We are investigating a five-cell design that will provide a higher efficiency. In addition, the tube will have solenoid focusing and incorporate a modulating anode. Table 2 gives an overview of the klystron specifications.

Table 2: Upgrade Klystron Specifications

| Operating Frequency | 1497 MHz               |  |

|---------------------|------------------------|--|

| Output Power        | 13.5 kW                |  |

| RF Gain             | 40 dB                  |  |

| Cathode Voltage     | -16 kV                 |  |

| Cathode Current     | 1.6 A                  |  |

| Klystron Efficiency | >55%                   |  |

| (target)            |                        |  |

| 3 dB Bandwidth      | 4 MHz                  |  |

| Cooling             | Low Conductivity Water |  |

| Focusing            | Solenoid Magnet        |  |

### **5 SUMMARY**

Prototyping the RF and digital sections is underway and we plan to test these sections together on a superconducting cavity in 2003. Discussions have begun with klystron firms regarding potential manufacturing. In addition we are collaborating with a number of other projects (RIA, TESLA, and Cornell) as a means of identifying common RF system elements that we can jointly develop and use. In the case of RIA we are developing the LLRF system as a generic system such that it is frequency-independent, accommodating multiple types of cavities. For the IR FEL upgrade the RF system will be able to control both the high  $Q_{\rm ext}$  linac cavities and the lower  $Q_{\rm ext}$ , high beam-loaded injector cavities.

#### **6 REFERENCES**

- [1] L. Harwood, "Upgrading CEBAF to 12 GeV", LINAC 2002, TH444, this conference.

- [2] Hovater et al, "RF Control Requirements for the CEBAF Energy Upgrade Cavities", Proc. LINAC 2000, Monterey CA, August 2000.

- [3] S. Simrock, "RF Control System for CEBAF", Proceedings of the 1991 Particle Accelerator Conference, San Francisco CA, May 1991.

- [4] J. Delayen, "Self Excited Loop", Proceedings of the SRF LLRF Workshop, Newport News VA, April 2001.

- [5] H. Dong et al., "A Dual Digital Signal Processor VME Board for Instrumentation and Control Applications", ICALEPCS 2001, San Jose CA, November, 2001.