## Synthesizer Controlled Beam Transfer from the AGS to RHIC

J. DeLong, J. M. Brennan, W. Fischer, T. Hayes, K. Smith, S. Valentino Brookhaven National Laboratory, Upton N.Y. 11973.

### Abstract

To ensure minimal losses and to preserve longitudinal emmittance, beam is transferred from the AGS to the RHIC bunch to bucket. This requires precision frequency and phase control for synchronization and kicker timing. The required precision is realized with a set of <u>Direct Digital Synthesizers</u>. Each synthesizer can be frequency and phase modulated to align the AGS bunch to the target bucket in the RHIC

#### 1 SYSTEM OVERVIEW

The RHIC low level RF system relies on DDS technology to generate the RF signals used to inject, accelerate and store beam in the Collider. To facilitate the generation of multiple revolution frequency harmonics a master oscillator running at 1024 times the revolution frequency is the clock input to the system synthesizers. This master oscillator also acts as the Voltage Controlled Oscillator in the RHIC RF servo loop. Therefore the system synthesizers are locked to the beam through this clock.

During the AGS to RHIC extraction process the two machines must be locked together in frequency and have a phase relationship that is precisely controlled. A signal derived from the RHIC master oscillator and equal to the bunch frequency of the AGS, acts as the reference oscillator in the AGS RF servo loop during synchronization and extraction.

Once locked a small frequency shift is added to the reference signal and the relative phase of the two machines begins to slip. When the correct amount of phase is accumulated, the AGS bunch will align or be "cogged" with the target bucket in the RHIC the frequency shift is then removed and the extraction kicker is triggered.

# 2 Direct Digital Synthesizers

A direct digital synthesizer is composed of four blocks: a 32 bit phase accumulator, sine look-up table, digital to analog converter and the anti-alias filter. The phase accumulator executes a discrete sum of the value in the delta phase register and the value of its output on each clock cycle. This yields a phase resolution of  $360^{\circ}$  /  $2^{32}$  for a 32 bit accumulator.

phase :=

$$\left(\text{phase }_{0} + \sum_{t} \delta \Phi\right) \text{ modulo}_{2}^{32}$$

$t := \frac{1}{\text{Fclock}}$

frequency :=  $\text{Fclock} \cdot \frac{\delta \Phi}{2^{32}}$

The output of the accumulator addresses a ROM that maps phase to amplitude, generating either a sine or cosine function. The ROM output is converted to an analog signal and the anti-alias filter removes unwanted spectral content [1].

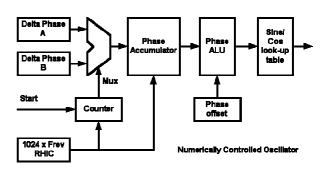

The key features of synthesizer technology are the resolution and continuity of the phase accumulator (1 part in 2<sup>32</sup>), the ability to hop between two frequency setpoints (fig. 1), and control of the absolute phase of the output.

Figure 1: Block diagram of the synchro synthesizer.

At reset the phase accumulator, and delta phase registers are set to zero and the output phase corresponds to the value in the phase-offset register (fig. 1). The output phase will remain unchanged until a setting for delta phase is latched into the phase accumulator. A common strobe is used to latch data into the phase accumulators of all the synthesizers in the RHIC RF system, this action guarantees that they have a consistent initial phase relationship and a common clock maintains a deterministic phase relationship thereafter.

### **3 SYNCHRONIZATION**

The RHIC injection synchronization system provides signals for the AGS servo loop reference, and the triggers for the extraction and injection kickers [2]. After the AGS

acceleration cycle has completed, the feedback loops switch from radial to synchronization control. The AGS bunch frequency is 19 times the RHIC revolution frequency. This is due to the 19/4 RHIC to AGS circumference ratio and the AGS RF harmonic number of 4. The synchro reference is set to harmonic 19 and coupled to the RHIC RF through the master clock.

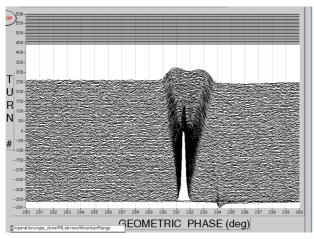

Figure 2: Beam debunching in RHIC.

As part of the setup process the AGS energy is adjusted to match that of RHIC. The revolution frequency in RHIC is precisely measured (~2 ppm) by observing the injected beam for 10 ms as it debunches with rf off (fig. 2). The rhic rf cavity frequency is set to this times 360 (28.023 MHz for gamma = 10.52) by setting the master oscillator frequency control word. The dipole field then in the AGS is adjusted such that the beam energy does not change while the bunch frequency is forced equal to 19 times the rhic revolution frequency. The beam radius in the AGS changes and the size of the extraction orbit bumps are compensated to keep the trajectory fixed in the transfer line. [3]

#### 4 COGGING

Cogging refers to the process of aligning AGS bunches with RHIC RF buckets. Adding an appropriate amount of phase to the synchro reference and the kicker clock, from which the kicker trigger is derived, realigns the two machines after each transfer. The cogging system is designed to support many different bunch fill patterns. An algorithm for calculating the phase advance of the two references as a function of fill pattern was developed:

$$\Delta \phi_{kicker} = 360^{\circ}$$

/ number bunches.

$\Delta \phi_{synchro} = (90^{\circ} + (19 / 4 \text{ x } \Delta \phi_{kicker})) \text{ x } 4.$

The phase advance for the synchro synthesizer rotates the next AGS bunch under the kicker and then must compensate for the advance of the RHIC kicker reference. The AGS target bunch is under the kicker on every fourth

revolution; therefore the kicker trigger is derived from 1/4 RHIC Frev.

The AGS transfers four bunches per pulse into the RHIC at 15 Hz. This requires the synchro system to advance the bunch phase and allow the feedback loop to settle in 66 2/3 ms. The phase is advanced by switching the synchro synthesizer to a frequency that is slightly lower than the revolution frequency of RHIC. This causes the phase of the AGS to slip with respect to RHIC. This frequency shift also drives the AGS to a new radius (fig. 2 bottom trace). A counter on the synthesizer clock applies the frequency offset for the correct amount of time to rotate the next bunch into position.

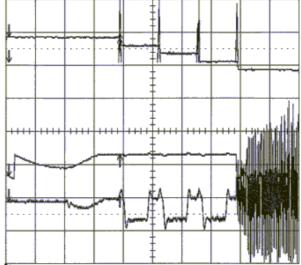

Figure 3: Beam current transformer, synchro loop error, and radial pickup in the AGS.

When the phase advance is complete the frequency and radius are returned to their nominal values and the kicker is fired.

## **5 IMPLEMENTATION**

#### 5.1 Hardware

The hardware consists of 3 Stanford Telecom 32 bit numerically controlled oscillators, and 2 counters. One oscillator defines the 360 RHIC buckets, this synthesizer drives the acceleration cavities. A second synthesizer generates the synchro-reference that is transmitted to the AGS. This DDS has a 32 bit counter that when triggered switches the synthesizers Delta phase register A to B for the programmed number of clock cycles. The third DDS is also configured with a counter and programmed to run at 1/4 Frev, this synthesizer determines the kicker position with respect to the 360 Frev synthesizer. These synthesizers are packaged in VME slave boards, and

controlled using Motorola Power PC  $\underline{F}$ ront  $\underline{E}$ nd  $\underline{C}$ omputers.

## 5.2 Software

The software is designed at two levels. The user chooses a fill pattern from a graphical interface and a time interval between injections (nominally 66 ms). The bunch pattern and time are passed to a function running on the front-end computer that calculates the values of frequency offset and the number of clock cycles to apply it. The high level software also sends information to the timing system so the kicker will be enabled the correct number of times to fill RHIC.

The function running on the FEC uses an iterative process to calculate the frequency offset and number of clock ticks to apply it:

N ticks = F clock x fill time. Delta F = Total Phase / N ticks.

The resolution of delta F is not infinite ( $\sim$ 6.5 mHz) therefore to consistently hit the zero crossing of the 360 Frev bucket the algorithm recalculates N ticks using the value of Delta F:

$N \ ticks = Total \ Phase / Delta \ F$ .

This same process is used for the kicker clock phase advance.

## **6 RESULTS**

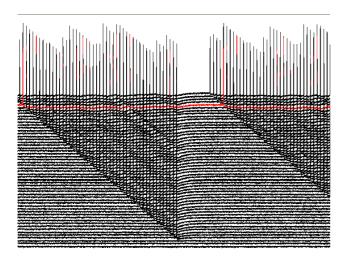

Figure 3: Waterfall display of wall current monitor in RHIC.

Figure 3 shows a waterfall display of 55 bunches injected into RHIC on a 60 bunch pattern. The horizontal scale shows 2 turns in RHIC and the kicker pulse triggers each

trace. The remaining gap is left unpopulated for the rise time of the abort kicker.

The cogging phase advance is accurate to  $2^{32}$  / delta F which is approximately 3  $\mu$  radians on the synchro reference this amounts to 60  $\mu$  radians at the RHIC bucket frequency thus adding no significant jitter to the AGS / RHIC extraction process.

#### REFERENCES

- [1] The DDS Handbook Fourth Edition, Editor Gwyn Edwards, Stanford Telecommunications Inc., 1994

- [2] J.M. Brennan et al, EPAC 1998.

- [3] N. Tsoupas et al. "Fast Extracted Beam (FEB) for the g-2 Experiment" C-A/AP/54