# SOLID-STATE MODULATORS FOR RF AND FAST KICKERS\*

E.G. Cook, G. Akana, E.J. Gower, S.A. Hawkins, B.C. Hickman, LLNL, CA 94550 C.A. Brooksby, Bechtel Nevada, Livermore, CA,94550 R.L. Cassel, J.E. De Lamare, M.N. Nguyen, G.C. Pappas, SLAC, Menlo Park, CA 94025

with pulse circuits and

#### Abstract

As the switching capabilities of solid-state devices increase, these devices are being incorporated into modulator designs for high voltage accelerator applications. Solid-state modulators based on inductive adder circuit topology have demonstrated great versatility with regard to pulse width and pulse repetition rate while maintaining fast pulse rise and fall times. Additionally, these modulators are capable of being scaled to higher output voltage and power levels. An explanation of the basic circuit operation will be presented as well as test data of several different hardware systems.

### BACKGROUND

The objective of this paper is to describe the design of solid-state modulators at LLNL and SLAC that are capable of meeting the diverse pulse requirements for two very different applications. In the first application, the modulator is used to drive high voltage klystrons to be used as sources for an RF linear accelerator. The second application requires modulators to drive fast kickers where a fast kicker is loosely defined as a beamline device, such as stripline kicker, that can be used to inject or extract a specific bunch into, or from, an accelerator that may have a large number of closely spaced bunches. The same basic modulator topology is used for both applications and the choice of specific solid-state devices is predicated on the specific application requirements.

There are a number of ways that solid-state devices may be used in such modulators. They can replace a closing switch, such as a thyratron or sparkgap, or they can be used to replace a switch with both closing and opening requirements such a vacuum tube as used in a hardtube modulator. This paper describes a modulator topology that conforms more to the later. Since most fast solid-state devices that have an opening capability are relatively low voltage, special circuit layouts are required to take advantage of their capabilities. One such circuit topology is an inductive adder.

## INDUCTIVE ADDER TOPOLOGY

An inductive adder is a circuit topology that utilizes multiple pulse transformers that have primary windings that are individually (and usually simultaneously) driven with pulse circuits and secondary windings that are electrically connected in series to generate the required high voltages. To achieve fast rise and fall times, the transformer must have very little leakage inductance: a requirement usually met by using a single turn primary winding and a single turn secondary. This results in the mechanical structure of the transformer being very similar to an induction cell used for a linear induction accelerator.

### Basic Circuit

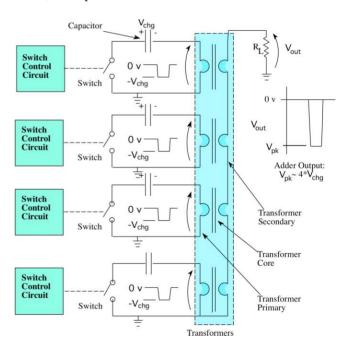

The basic circuit used to drive the transformers primary winding consists of a capacitor and a switch with the switch being connected between the capacitor and ground as shown in Fig. 1. In this circuit, the switch behaves like a vacuum tube in a hard-tube modulator: the switch is gated on to initiate the pulse and gated off to terminate the pulse. Any switch that can be gated on and off may be used in this circuit provided that it meets the performance requirements for the modulator with regard to pulse rise/fall time, pulse width, and repetition rate.

Figure 1: Basic 4-Cell Inductive Adder

In the primary-side circuit (Fig.1), the source impedance of the solid-state switch and the DC capacitor bank must be very low (<10hm). A small source impedance is required to be able to provide the total drive current (secondary current, any additional current loads in the primary

<sup>\*</sup> This work was performed under the auspices of the U.S. Department of Energy by University of California Lawrence Livermore National Laboratory under contract No. W-7405-Eng-48.

circuit, plus the magnetization current for the transformer core) without excess voltage droop during the pulse.

In this configuration, the output voltage on the secondary winding is the sum of the voltages appearing on each of the primary windings. This topology lends itself to being fabricated as a stack of modules whereby a module is defined to be a single pulse transformer and the drive electronics/energy storage for that transformer. When compared with other modulator circuits, the adder circuit topology has certain distinct advantages as well as issues and disadvantages as summarized below.

### Advantages:

All drive components are ground referenced No high-voltage grading of components required Output pulse format defined by programmable pulse generator and provides the capability of:

- pulse width agility

- burst frequency agility

- high burst frequency: >5 MHz

Modular consists of identical modules

- all modules switch same current

- all modules triggered simultaneously

- scaleable to higher voltages by adding modules

Low source impedance

- can drive wide range of load impedance

- load voltage is essentially independent of load impedance

### **Issues and Disadvantages:**

Each module must switch full load current

- may require many parallel components

- parallel switching devices must have low jitter on both turn-on and turn-off

Requires very small circuit loop inductance

Requires very fast opening switch that can interrupt

full load current and survive fault currents

Fault currents can be very large

Maximum output pulsewidth is limited to the saturation

time of the transformer

## Solid-State Switch Selection

Currently there are two solid-state devices that have been extensively used in inductive adder circuits: Metal Oxide Field Effect Transistors (MOSFETs) and Insulated Gate Bipolar Transistors (IGBTs). Both devices meet the basic requirement of being capable of being gated off at full current. For very short duration pulses at high repetition rates, the preferred components are MOSFETs. However, MOSFETs are limited in their peak operating voltage to 1000-1200V and to peak currents generally less than 100 amperes. Applications, not requiring the faster switching speeds of MOSFETs, can utilize IGBTs which are now available with voltage ratings of 6.5kV and are capable of switching peak currents in the kA range. The average power requirements for the gate drive circuits of either of

these devices are relatively small, although the peak currents required for fast turn-on and fast turn-off can be very demanding. The overall performance and capabilities of both types of devices is steadily improving as are those of other devices than can potentially be used in these circuits.

The gate drive circuit is also an essential element in achieving the best performance from the individual devices. The coupling between the drive circuit and the switch needs to have very low loop inductance, as the peak drive current required to achieve fast switching performance is on the order of tens of amperes. Even the devices within the gate drive circuit need to be very fast and have short turn-on and turn-off delay times. To achieve the fastest switching times each solid-state device requires its own dedicated gate drive.

## Basic Circuit Layout Considerations

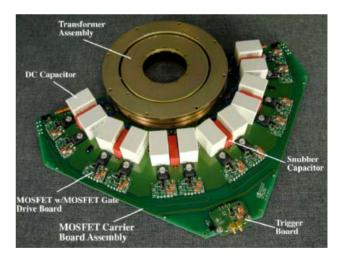

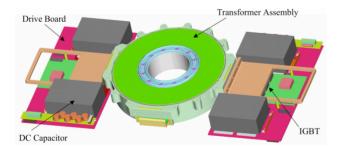

Essential to meeting fast pulse requirements, the inductance of the loop consisting of the transformer, capacitor, and switch must have a very small stray inductance. The voltage drop due to Ldi/dt degrades the pulse rise and fall time and the energy stored in the stray inductance can create voltage transients that affect the reliability of the solid-state switch. A very low stray inductance is achieved by using parallel arrays of both capacitors and solid-state devices. When these components are mounted on a printed circuit board (pcb), as shown in Fig.2, and wide traces are used for the interconnections, the total stray inductance can be reduced into the nanoHenry range and the pulser can demonstrate switching rates of  $50kA/\mu s$ . For the purpose

Figure 2: Drive Board/Transformer Module

of this discussion, let us assume that the switches shown in the simplified circuit schematic in Fig.1 are MOSFETs and have their source leads connected to ground. Choosing to have the sources connected to ground is very important since the gate drive circuit will also be ground referenced, thereby eliminating the need for floating and isolated power supplies. The pulse power ground and the drive circuit ground have a common point at the MOSFET source con-

nections but otherwise do not share common current paths: thereby reducing switching transients being coupled into the low-level gate drive circuits.

In this layout, the gate drive circuit is very tightly coupled (the loop inductance between the driver and switch are minimized) to the MOSFET so that very fast voltage transitions on the order of 10ns are achievable. The gate drive circuits are simultaneously gated on by signals from a single trigger board that is coupled to each gate drive by equal length transmission lines on the pcb.

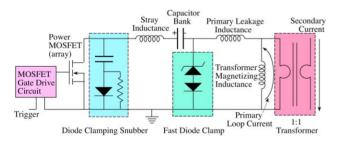

#### Transient Protection

Failure inducing voltage transients can be generated across the solid-state devices during turn-off. These transients are the result of energy stored in the stray circuit loop inductance, energy stored in the transformer primary, and/or voltage coupled into the primary circuit from the secondary (usually due to fault condition or trigger timing differences in stages of the adder). Transient voltage protection for the MOSFETs can be provided by several methods - two of which are shown in Fig.3. In the first method, a series combination of snubber capacitor and diode is tightly coupled to the MOSFET. The capacitor is initially charged to the same voltage as the DC capacitor bank. When the MOSFET is on, the diode prevents the snubber capacitor from discharging through the MOSFET. As the MOSFET turns off, transient voltages that exceed the voltage on the snubber capacitor turn on the diode so that the capacitor can absorb the excess energy. A resistor in parallel with the diode allows the excess capacitor energy to discharge into the DC capacitor between pulses or between bursts.

Figure 3: Drive Board Circuit with Transient Protection

A second method of transient protection is to place a diode clamp circuit consisting of a diode connected in series with a zener diode or transorb directly across the transformer primary winding. During diode conduction, the zener or transorb provides a small voltage drop so that the magnetic core can be properly reset as described in the next section. If the rest of the circuit layout is done properly, the transformer is the source of most of the circuit loop inductance and the diode clamp will provide a low impedance path for the magnetization current. This method also provides protection from other types of fault conditions. Good performance of either of the transient voltage circuits requires low inductance components, a low inductance layout

(usually a parallel array of components), and diodes with a low forward recovery voltage.

## Transformer Design

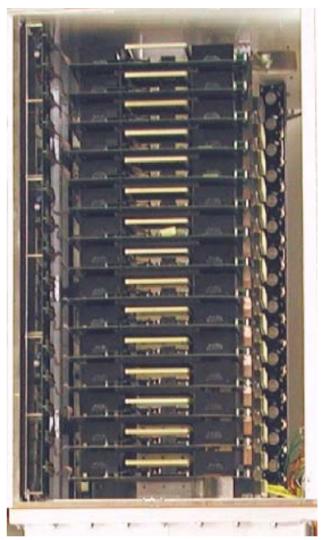

Minimizing the leakage inductance of the transformer primary winding is achieved by completely enclosing the magnetic core within a metal housing. If the gap of the primary turn is on the outside diameter of the magnetic core of toroidal geometry, the printed circuit board can be connected in this gap thereby creating a circuit loop with a very small stray inductance. The printed circuit board and transformer together form a modular unit, as shown in Fig. 2, that can be replicated and stacked vertically on the axial center as shown in Fig. 4. A metal rod through the center of the stack then forms the secondary turn for the assembly. The rod may be grounded at either end of the assembly to provide a pulse of either positive or negative polarity (or not be grounded and provide both a positive and negative polarity pulse simultaneously).

Figure 4: An Inductive Adder Subassembly

The selection of the magnetic core material is important but not critical. Materials having higher magnetic flux swing  $(\Delta B)$  allow the use of smaller transformer geometries where the geometry (specifically, the cross-sectional area) of the magnetic core is based on the volt-second product required to satisfy the pulse or burst requirements of the application. It is always prudent to have more material than is required to satisfy the minimum pulsewidth requirements (a saturating single-turn transformer is a very low impedance load and will result in very large and potentially catastrophic switch currents). Amorphous metal tape and nanocrystalline metal tapes have both been used as transformer cores with the nanocrystalline materials offering the lowest losses, albeit at a higher cost. Ferrite cores can also be used although their lower flux swing requires larger cross-sectional areas and therefore larger overall structures.

Not shown in the simplified adder circuit layout in Fig.1 is the reset circuit for the transformer cores. After normal pulse activity, the portion of the available  $\Delta B$  (voltseconds) used during the pulse must be restored so that the core does not saturate during subsequent pulses. This restoring process is performed by a reset circuit. If the modulator operates in a pulse burst format, or if the interval between pulses is long, a DC reset circuit can be used and is implemented by connecting a DC power supply through a large isolation inductor to the ungrounded end of the secondary winding of the adder stack. A DC current in the secondary winding will couple to all the transformers and induce a voltage across all the transformer primary windings (hence the need for the zener diode in the diode clamp circuit as mentioned in transient protection section) that will reset the magnetic cores. This approach is simple to incorporate and requires few additional components but has the disadvantage of requiring that the transformer have sufficient magnetic core material to sustain the entire burst stream. When the cores must be reset quickly between pulses, active (pulsed) reset applied to either the primary or secondary side of the transformer is used. Active reset circuits are more complicated than DC reset and usually require a controlled switch, charged capacitor, timing/trigger pulse and associated control circuitry as well as some circuit element to isolate the reset circuit from the high-voltage pulse.

### DARHT II KICKER MODULATOR

The DARHT II kicker modulator is designed to drive a fast dipole (stripline) kicker structure. This modulator exhibits the capabilities and performance of an inductive adder designed for fast, short duration pulses. The modulator requirements listed in Table 1 are met with a design that uses MOSFETs.

Table 1: DARHT II Pulser Requirements

| Parameter             | Requirement                     |

|-----------------------|---------------------------------|

| Output Voltage        | 20kV into 50Ω                   |

| Voltage Rise/Falltime | $\leq 10$ ns (10-90%)           |

| Flattop Pulsewidth    | 20ns to 200ns (continuously     |

|                       | adjustable)                     |

| Burst Rate            | 4 pulses @ 1.6MHz (~600ns       |

|                       | interval between leading edges) |

The kicker requires simultaneous positive and negative polarity pulses. These pulses are provided by two modulators that are identical in appearance and performance - the only difference is that the transformer assemblies are inverted in one of the modulators. One of the modulators with an adjoining rack that houses the control system, power supplies, diagnostics, and interfaces is shown in Fig.5.

Figure 5: DARHT II Kicker Modulator Assembly

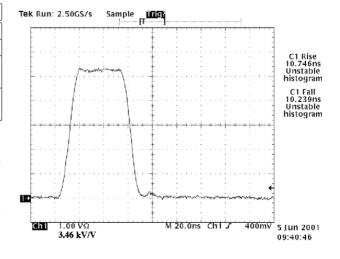

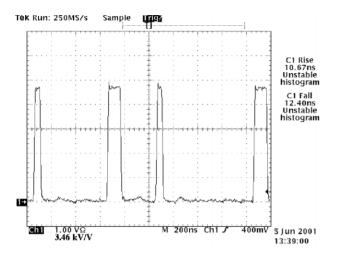

An example of the output pulse is shown in Fig. 6. This waveform is representative of the load voltage and has a rise and fall time just slightly greater than 10ns and a flattop ripple of  $\sim \pm 1\%$ . The peak di/dt on the rising edge is greater than 35kA/ $\mu$ s into  $50\Omega$ .

Figure 6: An 18kV Pulse of 30ns Duration

The pulse width agility and control of burst frequency is shown in Fig.7. The maximum burst frequency shown in this figure is  $\sim 2.5 \text{MHz}$  and the pulse width is varied in the range of 30ns to 120ns. In operation, the interval between adjacent pulses can be continuously reduced such that the pulses blend together. The timing for this system is generated by an arbitrary waveform generator.

Figure 7: A 4-Pulse Burst Demonstrating Both Pulse Width Agility and Variable Burst Frequency Within the Burst

### HIGH POWER KLYSTRON MODULATOR

The collaboration between LLNL and SLAC to design and build a very high power modulator demonstrates the flexibility of the inductive adder topology. This modulator is designed to drive a pair of 500kV klystrons. The modulator output is a  $3\mu s$  duration, 50kV, 6000A pulse into a 10:1 pulse transformer at a repetition rate of 120Hz. The circuit topology for this modulator is identical to the DARHT II modulator with the exception that the MOSFET array is replaced with 6.5 kV IGBTs. The current into the primary winding of each of the transformers in the inductive adder is provided by a pair of IGBT modules that operate at 4kV and each switch a peak current of  $\sim$  3kA. A drawing of one module of this modulator is shown in Fig. 8, with the complete assembly shown in Fig. 9.

Figure 8: A CAD Drawing of a Single Module

Figure 9: A 15 Cell Assembly of the SLAC Klystron Modulator

### **SUMMARY**

The solid-state switched inductive adder circuit topology is very versatile and is capable of satisfying the requirements for many short pulse applications. It has demonstrated a capability of producing short duration pulses at very high burst frequencies as well as longer pulses at very high peak and average power levels.

## **REFERENCES**

- [1] E.G. Cook, et al, "Design and Testing of a Fast, 50kV Solid-State Pulser," 2002 International Power Modulator Conference, Hollywood, CA, June 30-July 3, 2002.

- [2] E.G. Cook, et al, "Solid-State Modulator R&D at LLNL," RPIA Conference, Tsukuba, Japan. October 29-31, 2002.

- [3] R.L. Cassel, et al, "NLC Hybrid Solid State Induction Modulator," LINAC 2004, XXII International Linear Accelerator Conference, August 6-20, 2004.

641